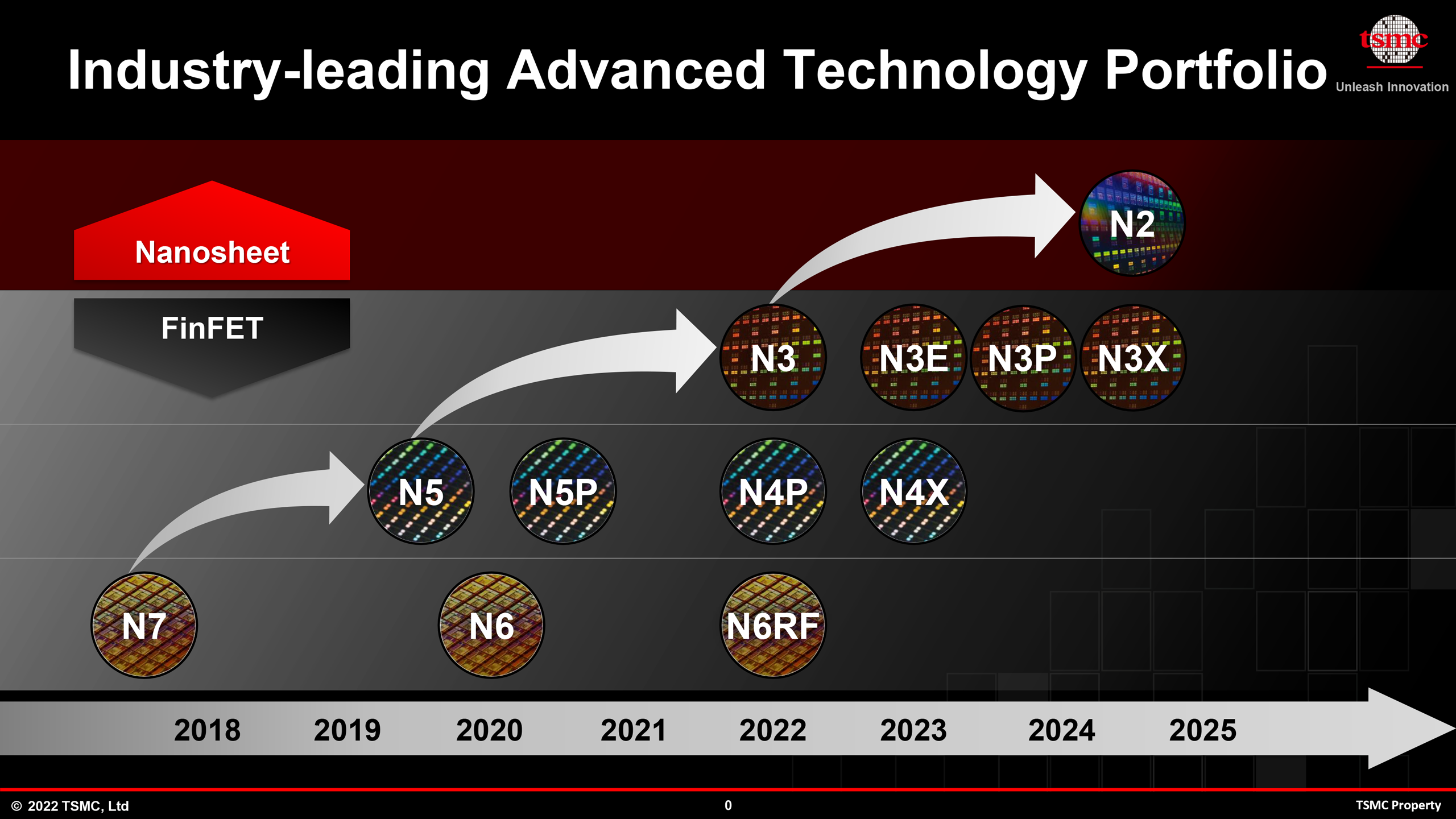

Taiwan Semiconductor Manufacturing Co. in the present day formally launched its N2 (2nm class) manufacturing know-how, its first node that can use gate-all-around field-effect transistors (GAAFETs), at its 2022 TSMC Know-how Symposium. The brand new fabrication course of will supply a full-now efficiency and energy advantages, however in the case of transistor density, it’ll barely impress in 2025 when it comes on-line.

Being an all-new course of know-how platform, TSMC’s N2 brings in two important improvements: nanosheet transistors (which is what TSMC calls its GAAFETs) and bottom energy rail that each serve the identical objective of accelerating performance-per-watt traits of the node. GAA nanosheet transistors characteristic channels surrounded by gates on all 4 sides, which reduces leakage; moreover, their channels could be widened to extend drive present and increase efficiency or shrunken to reduce energy consumption and price. To feed these nanosheet transistors with sufficient energy and now waste any of it, TSMC’s N2 makes use of bottom energy supply, which the foundry considers to be among the many greatest options to struggle resistances within the back-end-of-line (BEOL).

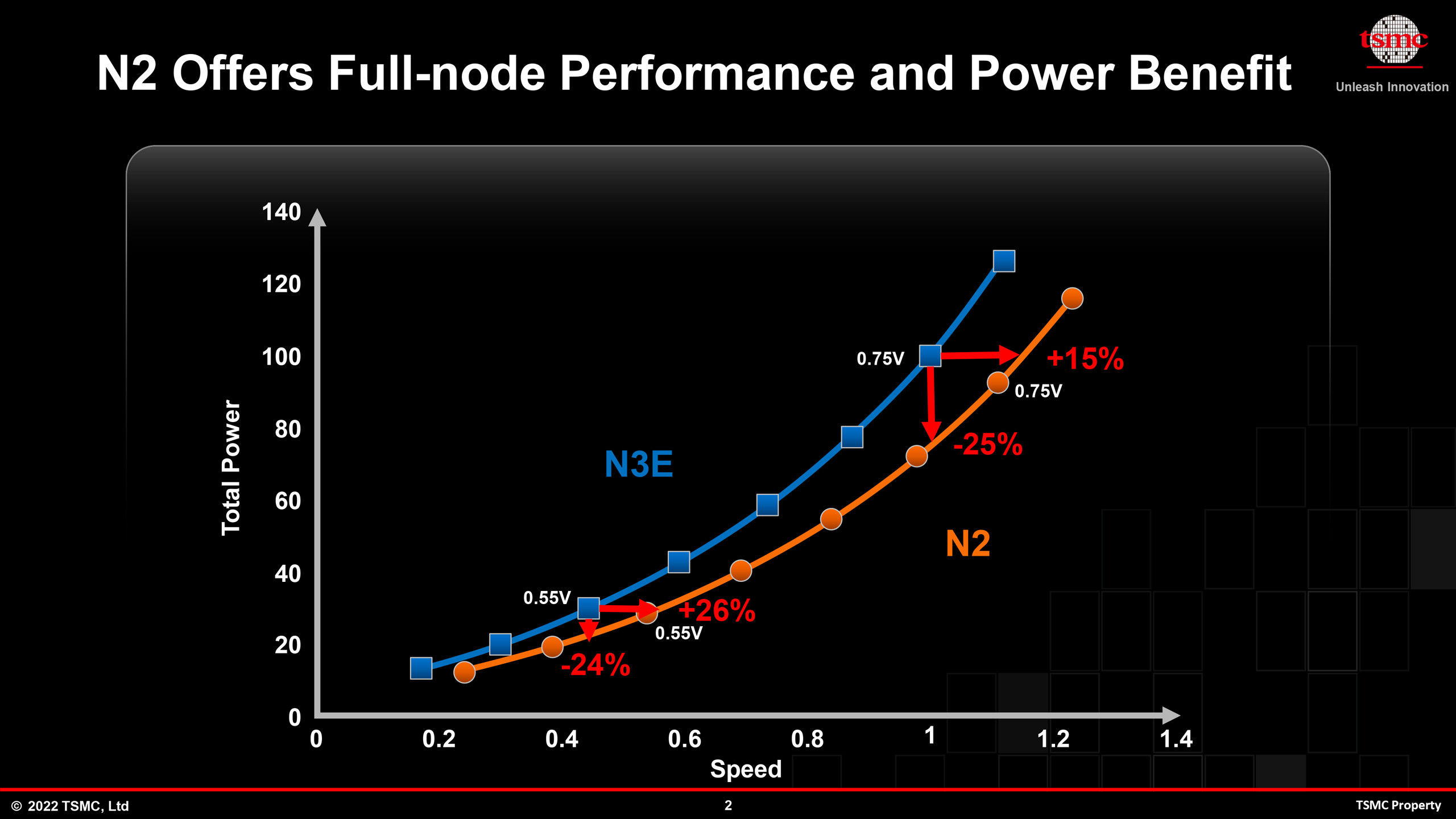

Certainly, in the case of efficiency and energy consumption, TSMC’s nanosheet-based N2 node can boast of a ten% to fifteen% increased efficiency on the identical energy and complexity in addition to a 25% to 30% decrease energy consumption on the identical frequency and transistor depend when in comparison with TSMC’s N3E. Nevertheless, the brand new node will increase chip density by solely round 1.1X in comparison with N3E.

| N2 vs N3E | N3E vs N5 | N3 vs N5 | N5 vs N7 | |

|---|---|---|---|---|

| Velocity Enchancment @ Identical Energy | 10% ~ 15% | +18% | +10% ~ 15% | +15% |

| Energy Discount @ Identical Velocity | -23% ~ -30% | -34% | -25% ~ -30% | -30% |

| Chip Density | >1.1X | 1.3X | ? | ? |

| HVM Begin | H2 2025 | Q2/Q3 2023 | H2 2022 | Q2 2022 |

Normally, TSMC’s N3 does supply full-node efficiency will increase and energy consumption reductions. However density-wise, the brand new know-how can hardly impress. For instance, TSMC’s N3E node gives a 1.3X chip density enhance over N5, which is a considerable enhance. For justice, we have to be aware that TSMC makes use of considerably convoluted ‘chip density’ metrics to explain transistor density on N3E and N2 in its supplies printed at its 2022 Know-how Symposium. Chip density basically describes a hypothetic chip consisting of fifty% logic, 30% SRAM, and 20% analog circuits. Fashionable designs are very SRAM intensive, however SRAM barely scales, identical to analog circuits; therefore an N2 chip that includes 50% of circuits that don’t scale will exhibit mediocre scalability in comparison with an N3E IC. If in comparison with N3S, a transistor-density optimized model of N3, the consequence may be even much less spectacular.

TSMC positions its N2 for numerous functions, together with cellular SoCs, high-performance CPUs, and GPUs. Among the many options of the N2 platform (along with GAA nanosheet transistors and bottom energy rail), the world’s No.1 foundry mentions ‘chiplet integration,’ which most likely implies that many functions that can use N2 may even use multi-chiplet packages to optimize efficiency and prices.

As reported, TSMC will start high-volume manufacturing of chips utilizing its N2 node within the second half of 2025, so making an allowance for how lengthy up to date semiconductor manufacturing cycles are, anticipate business 2nm chips to emerge in the marketplace solely in late 2025 or as a substitute in 2026. In fact, prior to now and in 2026, TSMC will supply a wide range of N3 (3nm class) nodes, however this can be a completely different story.