With the 2022 Flash Reminiscence Summit going down this week, not solely is there a slew of solid-state storage bulletins within the pipe over the approaching days, however the present can also be more and more a preferred venue for discussing I/O and interconnect developments as nicely. Kicking issues off on that entrance, this afternoon the OpenCAPI and CXL consortiums are issuing a joint announcement that the 2 teams can be becoming a member of forces, with the OpenCAPI commonplace and the consortium’s property being transferred to the CXL consortium. With this integration, CXL is about to change into the dominant CPU-to-device interconnect commonplace, as just about all main producers are actually backing the usual, and competing requirements have bowed out of the race and been absorbed by CXL.

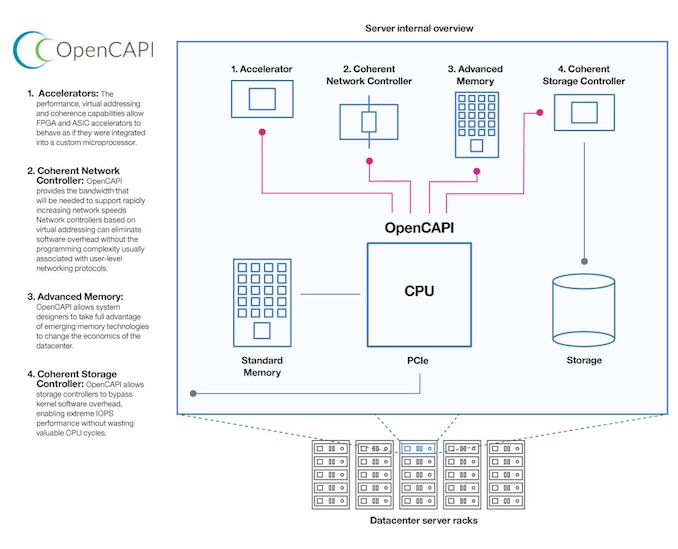

Pre-dating CXL by just a few years, OpenCAPI was one of many earlier requirements for a cache-coherent CPU interconnect. The usual, backed by AMD, Xilinx, and IBM, amongst others, was an extension of IBM’s present Coherent Accelerator Processor Interface (CAPI) expertise, opening it as much as the remainder of the trade and inserting its management below an trade consortium. Within the final six years, OpenCAPI has seen a modest quantity of use, most notably being applied in IBM’s POWER9 processor household. Like related CPU-to-device interconnect requirements, OpenCAPI was basically an software extension on high of present excessive velocity I/O requirements, including issues like cache-coherency and sooner (decrease latency) entry modes in order that CPUs and accelerators may work collectively extra intently regardless of their bodily disaggregation.

However, as one in all a number of competing requirements tackling this drawback, OpenCAPI by no means fairly caught hearth within the trade. Born from IBM, IBM was its greatest person at a time when IBM’s share within the server area has been on the decline. And even consortium members on the rise, resembling AMD, ended up skipping on the expertise, leveraging their very own Infinity Material structure for AMD server CPU/GPU connectivity, for instance. This has left OpenCAPI with no sturdy champion – and with no sizable userbase to maintain issues shifting ahead.

Finally, the will of the broader trade to consolidate behind a single interconnect commonplace – for the sake of each producers and clients – has introduced the interconnect wars to a head. And with Compute Categorical Hyperlink (CXL) shortly turning into the clear winner, the OpenCAPI consortium is turning into the newest interconnect requirements physique to bow out and change into absorbed by CXL.

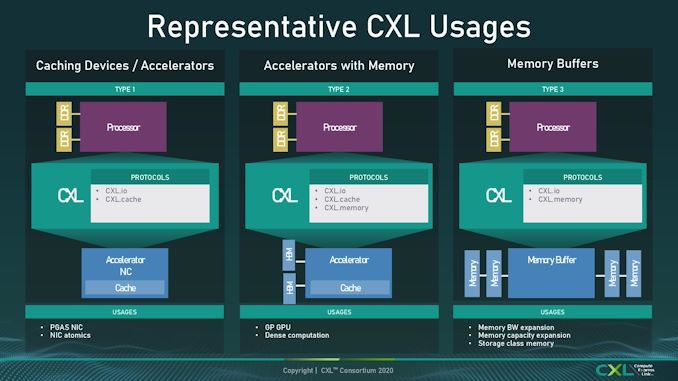

Beneath the phrases of the proposed deal – pending approval by the required events – the OpenCAPI consortium’s property and requirements can be transferred to the CXL consortium. This would come with the entire related expertise from OpenCAPI, in addition to the group’s lesser-known Open Reminiscence Interface (OMI) commonplace, which allowed for attaching DRAM to a system over OpenCAPI’s bodily bus. In essence, the CXL consortium can be absorbing OpenCAPI; and whereas they gained’t be persevering with its improvement for apparent causes, the switch signifies that any helpful applied sciences from OpenCAPI could possibly be built-in into future variations of CXL, strengthening the general ecosystem.

With the sublimation of OpenCAPI into CXL, this leaves the Intel-backed commonplace as dominant interconnect commonplace – and the de facto commonplace for the trade going ahead. The competing Gen-Z commonplace was equally absorbed into CXL earlier this 12 months, and the CCIX commonplace has been left behind, with its main backers becoming a member of the CXL consortium lately. So even with the primary CXL-enabled CPUs not delivery fairly but, at this level CXL has cleared the neighborhood, because it have been, turning into the only real remaining server CPU interconnect commonplace for the whole lot from accelerator I/O (CXL.io) to reminiscence enlargement over the PCIe bus.