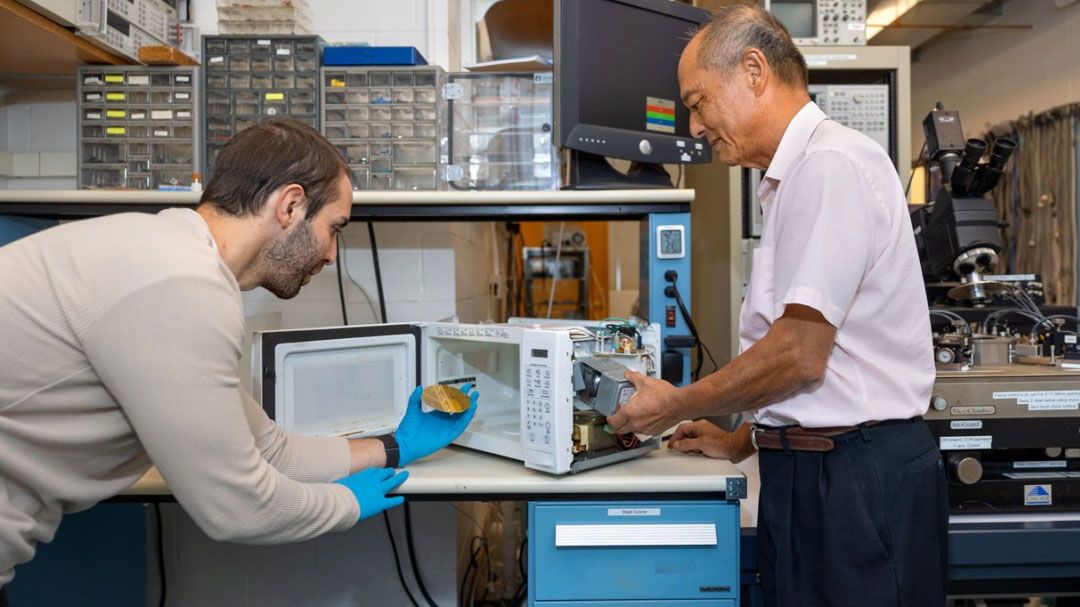

Scientists at Cornell College have been utilizing a modified family microwave oven to assist overcome a big impediment to sensible 2nm semiconductor manufacturing. The ensuing microwave annealer borrows inspiration from TSMC’s theories about microwaves and silicon doping with phosphorus. Consequently, semiconductor producers might push previous a earlier phosphorus focus restrict utilizing the newly devised tools and methods.

For semiconductor processes to proceed shrinking, silicon should be doped with increased and better phosphorus concentrations to facilitate correct and secure present supply. As issues stand, with the trade beginning mass manufacturing of 3nm elements, conventional annealing strategies are nonetheless working successfully. Nonetheless, because the trade reaches past 3nm, concentrations of phosphorus which are increased than its equilibrium solubility in silicon should be ensured. In addition to attaining increased focus ranges, consistency is significant in making useful semiconductor supplies.

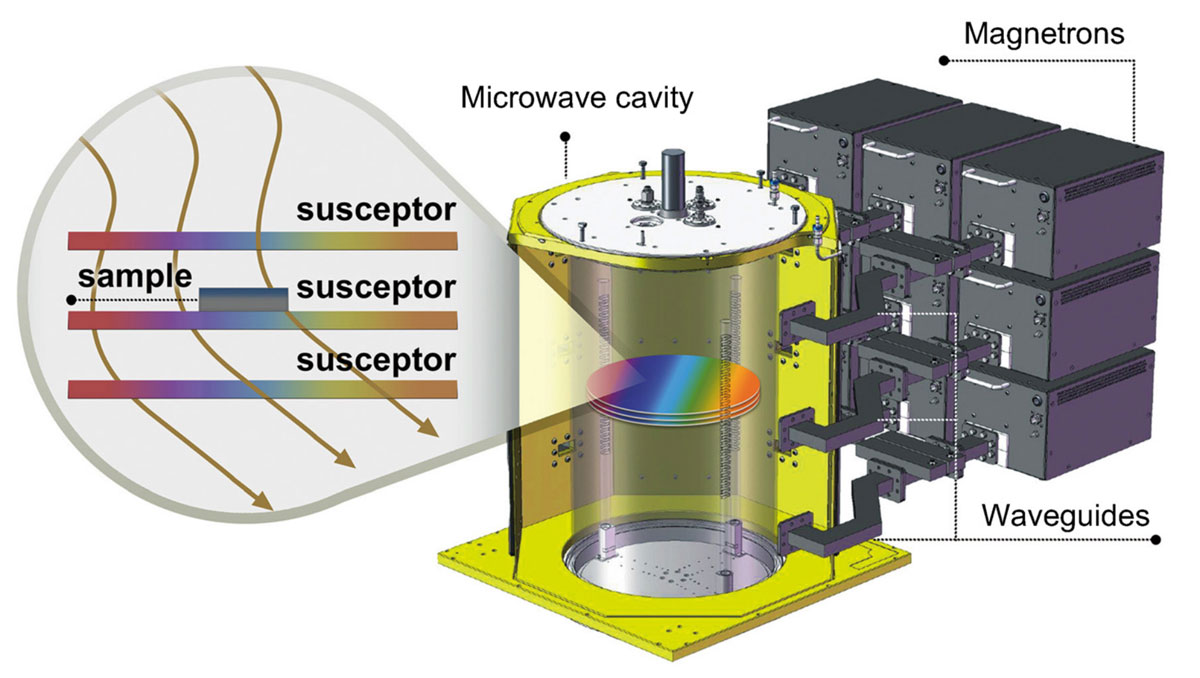

TSMC had beforehand theorized that microwaves may very well be used within the annealing (heating) course of to facilitate the elevated doping concentrations of phosphorus. Nonetheless, microwave heating sources beforehand tended to supply standing waves, that are dangerous for heating consistency. In easy phrases, earlier microwave annealing units heated their contents inconsistently.

Cornell College scientists acquired the backing of TSMC, and the Ministry of Science and Expertise of Taiwan, to conduct their analysis into microwave annealing. Of their ensuing scientific paper, shared by Cornell College earlier within the week, the scientists concluded they’d “overcome the elemental problem for top but secure doping above the solubility,” because of their superior microwave annealing strategies.