“Scorching Chips” is not simply the favourite snack of younger individuals—it is also the title of a technological symposium held yearly in Silicon Valley. We’re as much as the thirty fourth iteration of the gathering this 12 months, and Intel is amongst these attending with a handful of displays. There are some cool subjects, like “Heterogenous Integration Permits FPGA Primarily based {Hardware} Acceleration for RF Functions,” however the one we’re most fascinated about is about Foveros.

Foveros is the title for Intel’s progressive chiplet know-how. It differs from conventional 3D stacking in that it permits logic-on-logic stacking, which means that you would be able to have disparate sorts of processors stacked on each other. Intel can be making use of that functionality for its next-next-gen Meteor Lake processors, which can be its first chiplet-based (or “disaggregated”) processors.

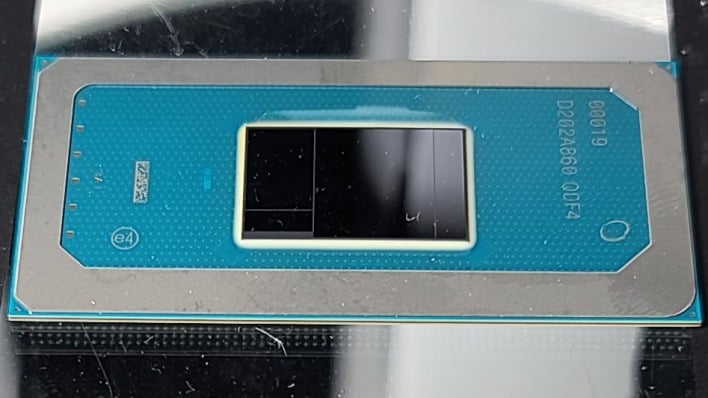

Diagram of Intel Meteor Lake processor with 6P+8E cores. Supply: Intel

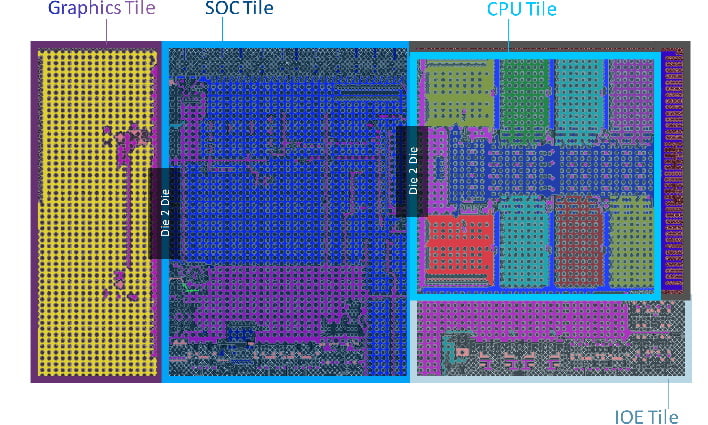

In preparation for its speak at Scorching Chips 34, Intel held a media roundtable the place it handed out (amongst different issues) this nifty little graphic that elaborates on what the disparate cube in Meteor Lake processors truly do. Leakers and lovers had just about put this info collectively already, but it surely’s at all times good to have official affirmation.

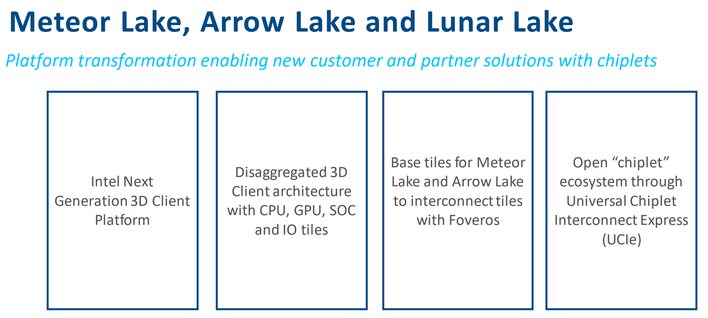

The precise speak, titled “Meteor Lake and Arrow Lake: Intel Subsequent Gen 3D Consumer Structure Platform with Foveros,” takes place tonight at 5:00 PM Pacific time. Nonetheless, there have been already just a few fascinating particulars divulged throughout the media roundtable.

Intel’s Boyd Phelps particularly stated that Meteor Lake is on schedule, which gave some within the media trigger to exhale after rumors got here out final week that Intel had cancelled a few of its 3nm orders with TSMC. An Intel roadmap from again in February appeared that Intel may very well be utilizing TSMC’s 3nm course of for Meteor Lake.

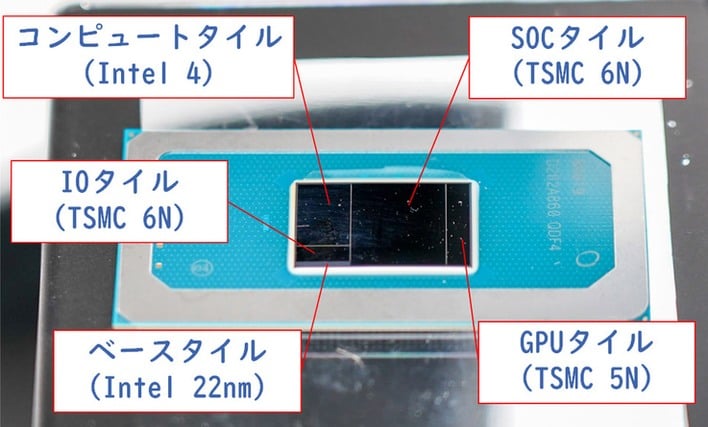

Impress PC Watch believes that is not the case, and stories as a substitute that it has the rundown on the processes that can be used for every chiplet. The positioning claims that the compute tile, the place the CPU cores stay, can be on Intel’s personal Intel 4 course of. What Intel calls the “IOE” and “SOC” tiles can be fabricated on TSMC’s 6N. In the meantime, the GPU tile will apparently be constructed on TSMC’s 5N. All 4 of those tiles will relaxation on a passive “base tile” fabricated on Intel’s 22FFL course of.

This use of a “base tile” is fascinating, and it is apparently one of many issues we’ll hear extra about at tonight’s presentation, together with further particulars relating to Intel’s disaggregated design technique in addition to extra details about Common Chiplet Interconnect Categorical, or “UCIe”. UCIe is meant to be an open commonplace for die-to-die connections on chiplet processors.

The aforementioned Boyd Phelps commented within the roundtable that UCIe will not be utilized in Meteor Lake nor within the Fifteenth-gen Arrow Lake processors, however that it’ll are available in “merchandise after Arrow Lake.” We would assume that that is going to be the previously-revealed Lunar Lake, which can be talked about within the header of the tile above.

It is doable that the presentation can be overwhelmingly a rehash of particulars we already know, however we suspect there may be a nugget or two of gold within the splash of particulars. We’ll be listening to the presentation this afternoon, and we’ll be certain that to let if Intel reveals something of word.