AMD 4th Gen EPYC Server CPU Roadmap And Efficiency Claims

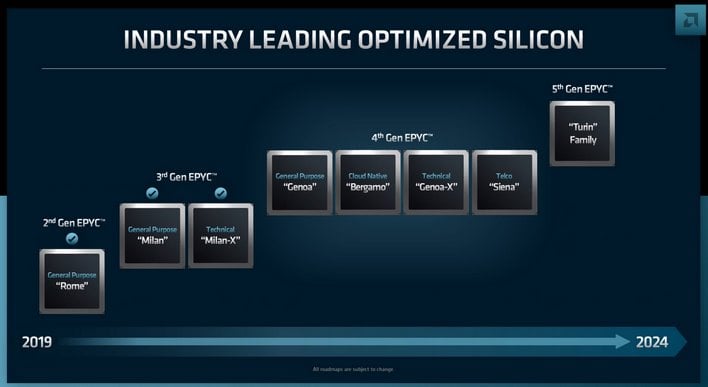

Beginning with its CPU silicon roadmap, AMD talked about what’s within the pipeline to succeed its third era EPYC Milan (common goal) and Milan-X (technical) processors. As you’ll be able to see within the above roadmap, AMD’s 4th gen EPYC household can be comprised of Genoa (common goal), Bergamo (cloud native), Genoa-X (technical), and Siena (telecommunications), adopted by its fifth gen EPYC Turin launch in 2024.

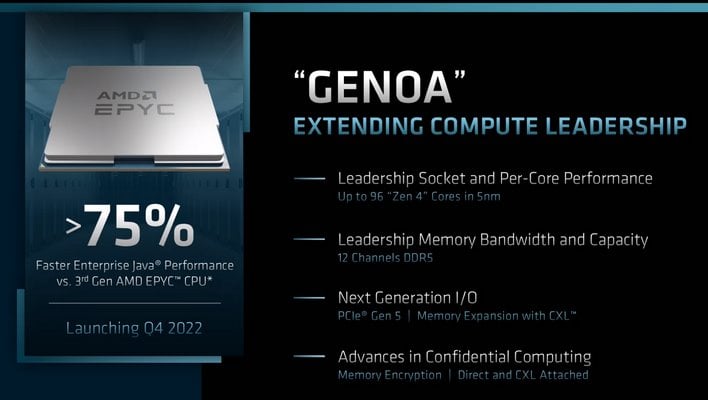

In accordance with AMD, Genoa is poised to be the highest-performance general-purpose server processor in the marketplace—the corporate claims its top-of-the-stack silicon will ship a better than 75 p.c uplift in enterprise Java efficiency in comparison with its high third gen EPYC processor.

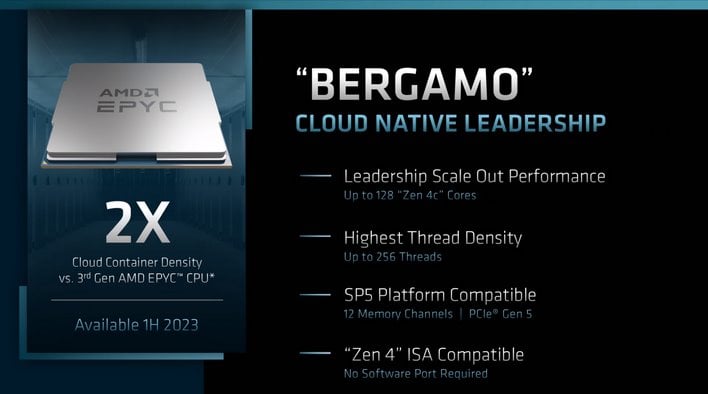

Genoa is on observe to launch within the fourth quarter. Then within the first half of 2023, AMD will launch its Bergamo stack powered by what the corporate is dubbing Zen 4c. Likewise, AMD is pitching Bergamo because the highest-performance server processors for cloud native computing.

Bergamo relies on the Zen 4 ISA, however will throw extra cores and threads at cloud purposes. Particularly, Bergamo will max out at 128 cores and 256 threads.

AMD beforehand stated Bergamo will stay totally software program suitable and make the most of the identical socket platform as Genoa, and assist the identical applied sciences (like DDR5 and PCIe 5). Nevertheless, it is going to additionally embody a set of cloud enhancements, corresponding to a density-optimized cache hierarchy and higher energy effectivity for cloud-native workloads.

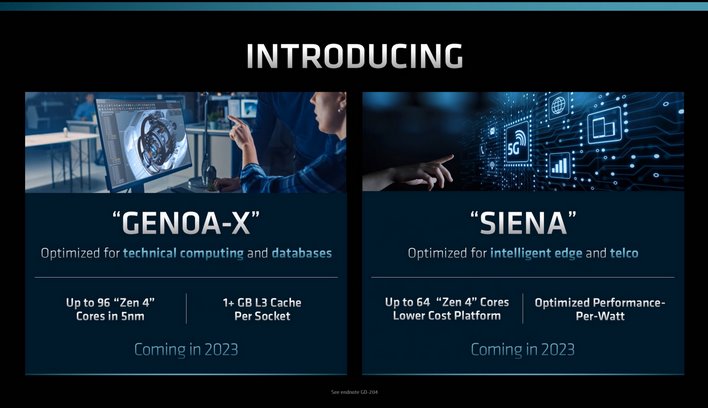

Trying a bit additional down the road, AMD revealed it is going to have two different 4th gen EPYC iterations in 2023, these being Genoa-X and Siena. Genoa-X include as much as 96 cores and 192 threads similar to Genoa, and make the most of the identical SP5 socket (LGA 6096), however will characteristic 1GB or extra of L3 cache per socket. Like Milan-X, AMD is concentrating on clients who must energy by means of workloads that thrive on L3 cache.

As for Siena, it is going to wield as much as 64 Zen 4 cores, although past that we don’t have a ton of particulars to share. All we actually know is what’s said within the slide, which is that it’s optimized for performance-per-watt and can be pitched as a lower-cost platform for clever edge and telecommunications markets.

Search for extra particulars on Genoa-X and Siena as their respective launches come nearer into view.

AMD Intuition MI300 Fuses Zen 4 CPU Cores With CDNA 3 Graphics

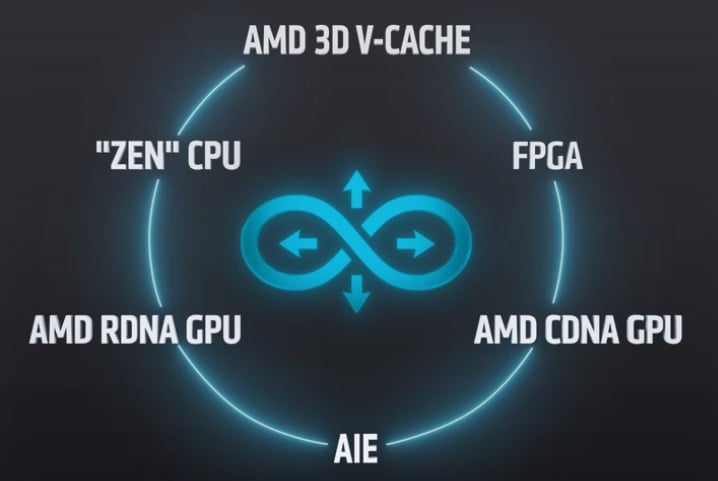

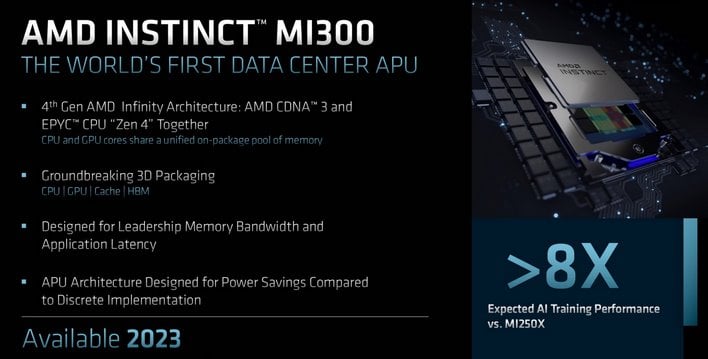

One of many messages AMD delivered robust and clear throughout the occasion that it is graphics IP is strongly positioned throughout virtually each market phase, together with cell, embedded, consoles, PC, and naturally the info middle. Not solely does this give AMD a broad market to handle, it additionally allows merchandise that faucet into each its CPU and GPU architectures, as is the case with its upcoming Intuition MI300 based mostly partly on its upcoming 5nm CDNA 3 structure.

The Intuition MI300 is being billed because the world’s first information middle APU. Leveraging what AMD describes as a “groundbreaking 3D chiplet design,” the info middle APU combines CDNA 3 graphics cores with Zen 4 CPU cores on the identical package deal, together with each cache reminiscence and HBM chiplets to spherical issues out.

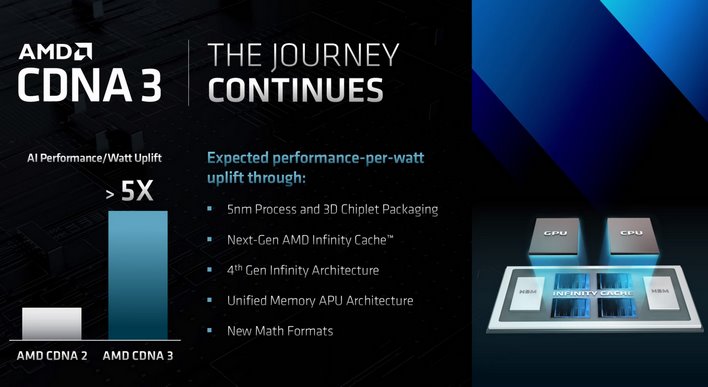

Simply as RDNA 3 is coming to ship a brand new era of desktop and laptop computer graphics options for gaming, CDNA 3 will observe go well with within the information middle someday subsequent 12 months, with AMD promising a five-fold soar in performance-per-watt on AI workloads in comparison with CDNA 2.

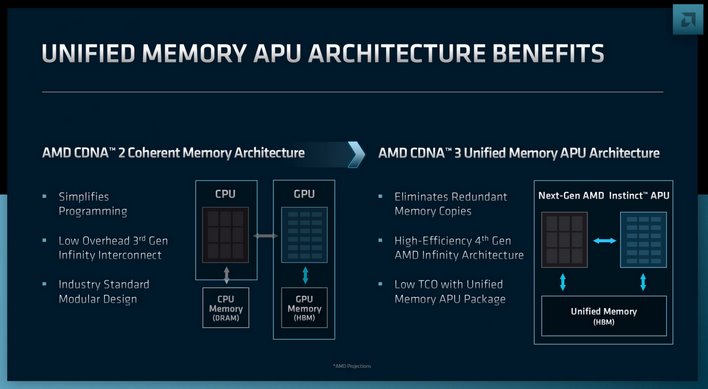

CDNA 3 can be manufactured on a 5nm course of and make the most of 3D chiplet packaging. It should additionally mark a shift away from a coherent reminiscence structure to a unified reminiscence APU structure, which guarantees to make it extra environment friendly. Going this route eliminates redundant reminiscence copies by taking away the necessity to copy information from one pool to the opposite.

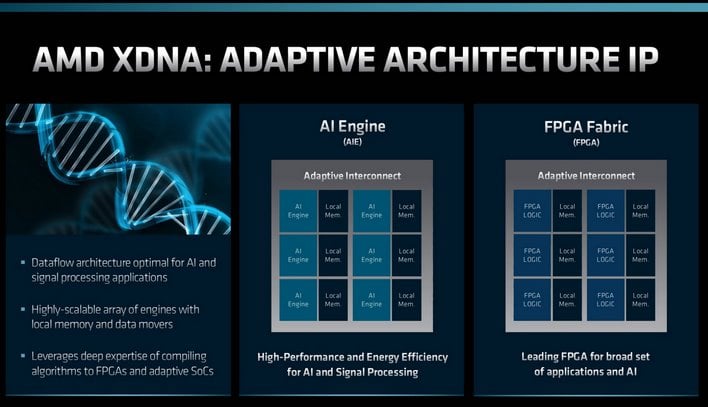

“The FPGA material combines an adaptive interconnect with FPGA logic and native reminiscence, whereas the AIE supplies a dataflow structure optimized for top efficiency and power environment friendly AI and sign processing purposes. AMD plans to combine AMD XDNA IP throughout a number of merchandise sooner or later, beginning with AMD Ryzen processors deliberate for 2023,” AMD says.