Actual-Time Methods (RTS) proclaims the upcoming availability of its new RTS Secure Hypervisor. The RTS Secure hypervisor can be an OS unbiased useful security licensed Sort 1 hypervisor to focus on mixed-critical workloads based mostly on x86 multicore processor applied sciences and can be obtainable worldwide.

The brand new RTS Secure Hypervisor can be delivered as an entire OEM bundle, bundling the licensed real-time hypervisor with functionally secure and non-safe digital machines and a licensed secure OS such because the Linux-based Zephyr or QNX. This bundle targets any off-the-shelf or custom-specific embedded computing platform outfitted with FuSa-capable x86 processors. The primary implementations can be based mostly on Intel Atom x6000E Collection processors with built-in Intel Security Island and eleventh Technology Intel Core processors.

“We need to be certain that engineers get essentially the most environment friendly route to totally functional-safety-compliant functions by using pre-certified platforms. Secure real-time hypervisor expertise is the important thing to tying every little thing collectively, from secure {hardware}, secure Sort 1 grade digital machines, and secure OSes to non-safe domains working multi-purpose OSes. In the long run, software engineers solely must deal with their safety-critical software half to achieve useful security certification. That is ultra-convenient in an IoT- and AI-driven decade, the place many inventions are rising within the autonomous car and collaborative robotic sectors, for instance. Right here the core features should adjust to useful security requirements. The non-safe a part of the bundle, however, might be modified and up to date as wanted with out affecting the functionally secure components in any manner. And the actual candy spot for engineers is that they’ll make the most of customary x86 applied sciences,” says Michael Reichlin, CEO at Actual-Time Methods, to elucidate the gross sales technique for the brand new RTS Secure Hypervisor.

Typical mixed-critical functions

Typical mixed-critical functions embody full options on a single embedded computing platform that mix real-time enabled secure controls with non-safety functions – resembling GUIs, AI logic or imaginative and prescient and situational consciousness methods. With the Business 4.0 development, IoT gateways have gotten more and more embedded. Built-in gateways are required, for superordinated management logic over real-time 5G and/or for something associated to the IT/OT fusion development to allow predictive upkeep and new enterprise fashions through agile subscriptions with pay-per-use and usage-based pricing.

Advantages of mixed-critical software engineering

OEMs using a single {hardware} platform for mixed-critical software designs profit from price financial savings resulting from a lowered system depend, leading to an improved imply time between failures (MTBF) in comparison with multi-system installations. One other profit is that engineers can handle vital and non-critical functions on one single chip or {hardware}, which eases software engineering and testing and information change between these functions. And regardless of the single-system strategy, such a hypervisor implementation permits all non-safety functions to be constantly up to date and modified with out recertifying the safety-relevant parts. This isn’t simply necessary for innovation but in addition for enhancing cyber safety.

Goal markets for mixed-critical software

Goal markets for the brand new RTS Secure Hypervisor are collaborative robotics, industrial automation, autonomous automobiles, medical gear, building and agricultural equipment, and rail transportation. Goal certifications embody IEC 61508 for safety-related embedded methods because the baseline (for all SIL ranges) in addition to ISO 13849 for the protection of equipment (as much as PL e), IEC 62304 for medical system software program (as much as Class C) and EN 50128 for railway (as much as SIL 4). Lastly, cyber safety certifications resembling IEC 62443 4 for industrial automation and management methods may also be lined.

The characteristic set intimately

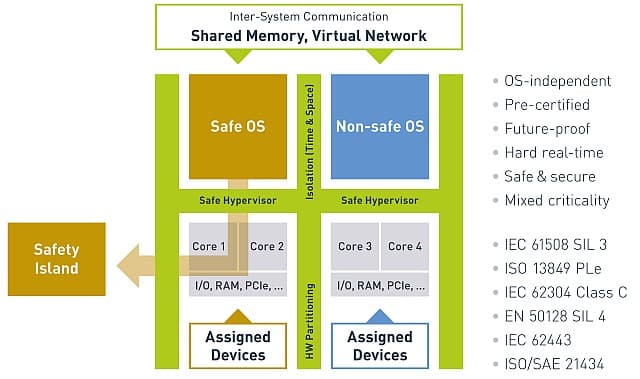

The brand new RTS Secure Hypervisor is designed as a Sort 1 real-time hypervisor that avoids including latency to the secure OS. The secure OS can have direct and unique entry to the allotted {hardware} assets. Communication between the totally different mixed-critical functions and processes is ensured by functionally secure shared reminiscence and/or digital Ethernet channels. The supported secure OSes can be QNX and Zephyr, mixed with Linux or different customary x86 real-time working methods for non-safe functions. The hypervisor will assist on-chip Intel Security Island as built-in within the Intel Atom x6000E Collection processors or exterior secure logic for Intel Core and Xeon processors. At the very least two cores are required to deploy the brand new functionally secure hypervisor, in addition to PCIe pass-through to solely assigned units. At least, a quadcore processor is due to this fact really helpful to have the ability to host non-critical functions as effectively.

Clients can simply combine the devoted boot loader, the RTS Secure Hypervisor, and their secure OS. Most snug is that there is no such thing as a must compile or re-build the hypervisor software program because the configuration solely must be written to a plain-text configuration file. Clients resolve whether or not the hypervisor and secure OS are locked into the firmware – making it a part of the board – or securely loaded from storage units resembling eMMCs. Non-safe Linux OS implementations on digital machines might be deployed and modified by OEMs as wanted.