Once we begin speaking about processor efficiency, it is essential to know that numerous functions have a wide range of wants. It goes past easy “latency vs. throughput” issues. There are various elements that go into truly executing a program that every one affect the way it performs.

Whereas we are inclined to assume “serial code = CPUs” and “parallel code = GPUs”, there are some duties which might be greatest executed on CPUs, but nonetheless want large quantities of reminiscence bandwidth and large caches, or code that’s virtually fully crunchy floating-point compute with minimal I/O. Notably within the HPC world, yow will discover plenty of these unique workloads that merely do not run that nicely on typical techniques owing to their uncommon calls for.

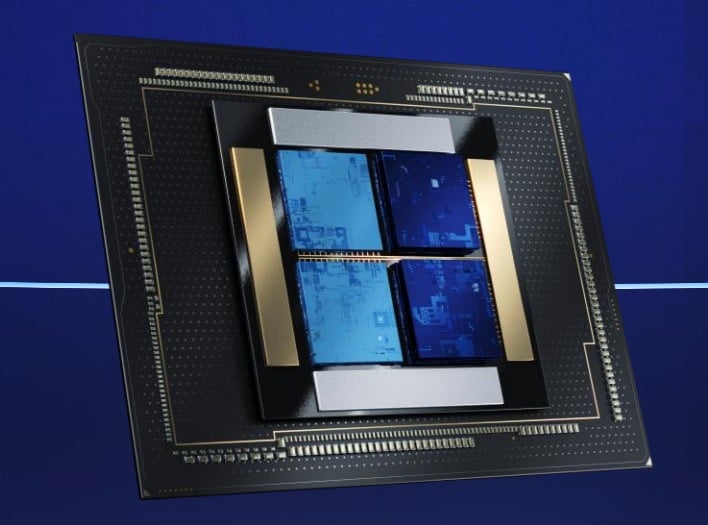

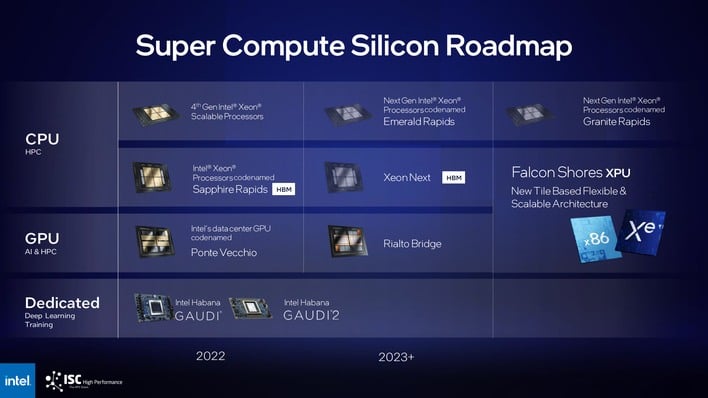

Sapphire Rapids With HBM For HPC Workloads

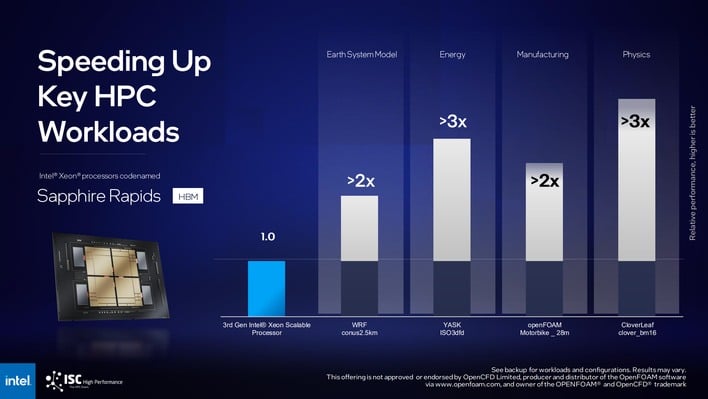

First up: the Sapphire Rapids numbers. The entire data that Intel printed got here within the type of relative comparisons towards its present, third-generation Xeon Scalable components. Total, it looks as if Intel is promising between double and triple the efficiency from its upcoming HBM-equipped chips in comparison with the extant fashions. That is a heck of so much higher than the standard gen-on-gen will increase we’re used to.

Ponte Vecchio hasn’t truly debuted as a industrial product but, however which may be partly as a result of Intel is delivery each obtainable bundle it might fabricate to Argonne Nationwide Laboratory in Illinois. There, Intel and Cray are constructing the Aurora supercomputer that Intel guarantees will surpass the just-launched Frontier machine powered by rival AMD. AMD beat Intel to the punch with the primary “exa-scale” machine, so Intel’s going to punch again by doubling Frontier’s efficiency.

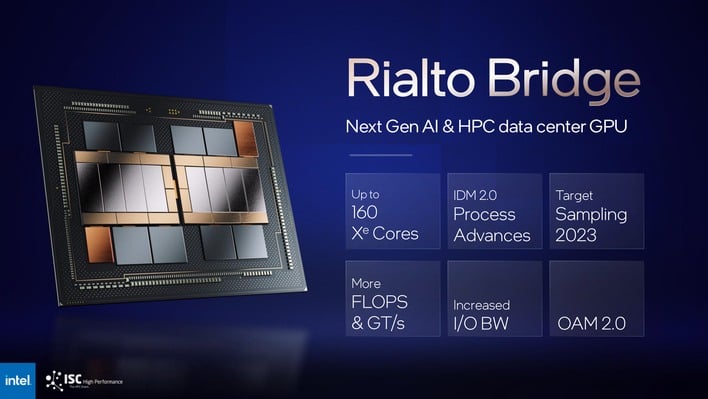

Rialto Bridge Will Supplant Ponte Vecchio

The successor to Ponte Vecchio will probably be referred to as Rialto Bridge. Intel divulged little details about the upcoming processors, however there are just a few tidbits to pay attention to. The place Ponte Vecchio tops out at 128 Xe cores, Rialto Bridge will apparently sport as much as 160 cores.

That, clearly, means extra compute throughput, however Intel can also be promising elevated reminiscence bandwidth (by way of “extra GT/s”, that means a better reminiscence clock) in addition to “elevated I/O bandwidth.” Ponte Vecchio already makes use of PCIe 5.0, and it is pretty unlikely that they are speaking about PCIe 6.0. As an alternative, Intel might be speaking about its personal Xe Hyperlink interconnect, the analog to NVIDIA’s NVLink.

The blue workforce additionally notes that Rialto Bridge will convey assist for the second revision of the Open Accelerator Module (OAM) socket specification. OAM is a part of an try (often called OAI) to outline a typical specification for compute accelerators, together with type issue, baseboard, socket, and so forth. OAM v2 specifies a rise in energy supply as much as 800 watts.

Intel’s Highly effective Falcon Shores XPU

After Rialto Bridge and Emerald Rapids, Intel will probably be launching a product codenamed “Falcon Shores.” Intel refers to Falcon Shores as an “XPU”, and that is as a result of it is neither CPU nor GPU, however each—or maybe “both” may be extra applicable. Primarily, it is a processor that may combine and match Xeon CPU tiles and Xe GPU tiles to supply the right steadiness of compute efficiency for all kinds of workloads.

Even for a product that is not launching till 2024 on the earliest, these are some fairly daring claims, however given Intel’s aggressive scheduling for its manufacturing division, they do not sound unrealistic. If Intel can sustain the tempo, its opponents might have their work minimize out for them.